Portable and Scalable Compilation for CGRA Accelerators

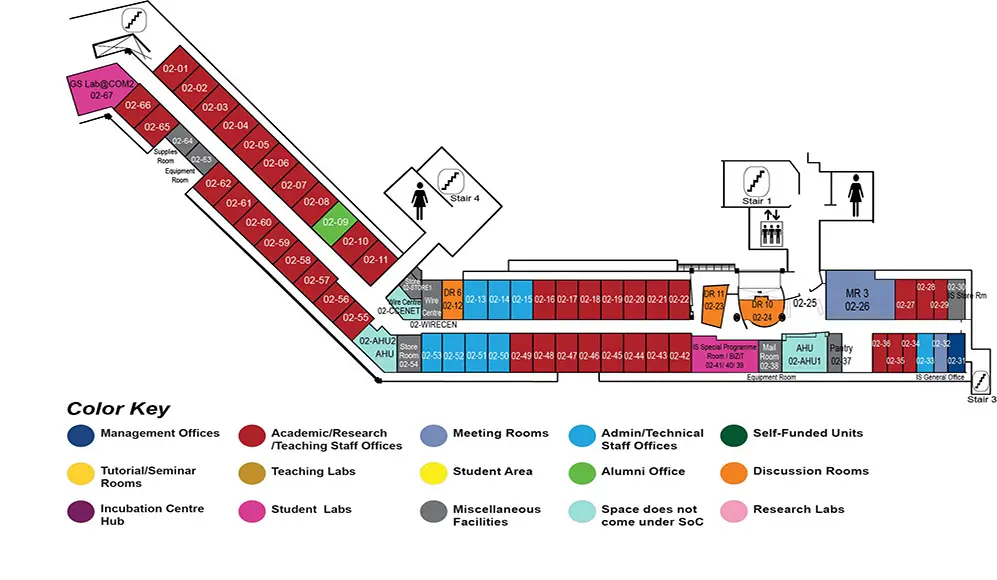

COM2 Level 2

MR3, COM2-02-26

Abstract:

Coarse-Grained Reconfigurable Array (CGRA) is a software-defined hardware accelerator and provides a promising pathway to scale the performance and power efficiency of computing systems while offering excellent flexibility. Due to the high-level programmability of the hardware units, the accelerator requires an effective compiler to fully realize their potential. This thesis introduces portable and scalable compiler techniques for CGRAs. The proposed compiler generates efficient application-level mapping for diverse accelerators, advancing their evolution and adoption. The challenge with a new accelerator is that the designer needs to manually tune the compiler to adapt to the accelerator characteristics. This thesis presents a portable compiler LISA that can automatically tune the parameters using learning to adapt to the features and nuances of the hardware. Existing mappers are difficult to handle complex data dependency to generate optimal mapping. We propose a routing-centric mapping paradigm, Rewire, which can share the routing information among multiple data-flow graph nodes to guide simultaneous multi-node mapping. To generate high-quality application-level mapping, we present ChordMap, generating a spatio-temporal mapping for multiple kernels in an application. ChordMap judiciously employs concurrent execution of multiple kernels to improve parallelism and thereby maximize throughput. Moreover, the compiler needs to coordinate with the architectural design to fully exploit the potential of a CGRA accelerator. Towards this end, we integrate the portable compiler into our comprehensive design framework, Morpher, which provides a unified representation connecting the compiler and the hardware architecture generator. Compared to state-of-the-art techniques, our solution generates more efficient mapping on CGRAs and is integrated with an end-to-end toolchain. We believe that the approaches proposed in the thesis will serve as a foundation for the future development of CGRA systems.